市場(chǎng)傳出���,為降低成本,聯(lián)發(fā)科明年新芯片高階制程開(kāi)發(fā)計(jì)劃有所變動(dòng)�,將暫緩7納米制程進(jìn)度�����,最高階只到12納米�����,并以16納米為主����。聯(lián)發(fā)科明年主力芯片訂價(jià)是否能優(yōu)于對(duì)手高通,仍有待密切觀察����。

聯(lián)發(fā)科一向不對(duì)產(chǎn)品進(jìn)度與客戶事宜評(píng)論。據(jù)悉����,聯(lián)發(fā)科明年第1季將推2款P系列新芯片�,代號(hào)為P40與P60,采12納米制程生產(chǎn)���。就明年全年開(kāi)案進(jìn)度而言��,聯(lián)發(fā)科新芯片都將集中在中低階芯片,高階芯片及采先進(jìn)制程生產(chǎn)的產(chǎn)品��,進(jìn)度反而暫緩����,其中,7納米至目前為止都沒(méi)有任何新開(kāi)案進(jìn)度�。

業(yè)界傳出,聯(lián)發(fā)科為節(jié)省先進(jìn)制程高昂的光罩費(fèi)用�,明年新芯片都將以16納米為主要投產(chǎn)制程,借此降低成本�����,擠出更多潛在獲利��,也符合共同執(zhí)行長(zhǎng)蔡力行過(guò)去習(xí)換降低成本減少研發(fā)支出的作風(fēng)�。

據(jù)了解���,聯(lián)發(fā)科內(nèi)部定調(diào)�����,明年先進(jìn)制程芯片�����,最高只用到臺(tái)積電12納米制程�,同時(shí)聯(lián)發(fā)科將持續(xù)分散晶圓代工來(lái)源,將部分芯片持續(xù)轉(zhuǎn)交聯(lián)電生產(chǎn)����,以尋求較好的利潤(rùn)空間�����。

業(yè)界解讀����,這是蔡力行上任后���,在樽節(jié)成本上的明顯作為,雖然蔡力行未大刀闊斧樽節(jié)人力成本支出�,但在研發(fā)與新芯片開(kāi)發(fā)進(jìn)度上,明顯開(kāi)始縮手�����。蔡力行先前股東會(huì)后也曾說(shuō)過(guò)�,不具優(yōu)勢(shì)的產(chǎn)品就會(huì)減少投資,專(zhuān)注在有獲利空間的產(chǎn)品上��,從到目前為止���,聯(lián)發(fā)科未有任何7納米制程產(chǎn)品就可窺知此策略方向����。

聯(lián)發(fā)科日前發(fā)表P23與P30芯片���,預(yù)計(jì)第4季出貨��,2顆芯片都采用16納米制程生產(chǎn)�,由于臺(tái)積電代工價(jià)格仍比三星高�����,導(dǎo)致聯(lián)發(fā)科訂價(jià)空間遭勁敵高通擠壓�����。不過(guò)�����,相較之下,聯(lián)發(fā)科采16 納米制程生產(chǎn)芯片�����,良率較高�,對(duì)整體獲利仍可望帶來(lái)助益。

至于明年第1季上市的P40與P70芯片�,聯(lián)發(fā)科都將采用12納米生產(chǎn)�,目標(biāo)是要爭(zhēng)取OPPO R系列新機(jī)訂單,搶攻明年中階市場(chǎng)�。據(jù)悉, P40芯片定價(jià)將落在15至16美元��,對(duì)應(yīng)到高通S640芯片���。市場(chǎng)人士指出,若明年P(guān)40與P70芯片銷(xiāo)售繳出佳績(jī)��,聯(lián)發(fā)科12納米生產(chǎn)的比重才會(huì)顯著增加����。

先進(jìn)工藝制程成本的變化是一個(gè)有些爭(zhēng)議的問(wèn)題�����。成本問(wèn)題是一個(gè)復(fù)雜的問(wèn)題,有許多因素會(huì)影響半導(dǎo)體制程成本���。本文將討論關(guān)于半導(dǎo)體制程的種種因素以及預(yù)期���。

影響半導(dǎo)體工藝制程成本的第一個(gè)因素是晶圓成本。

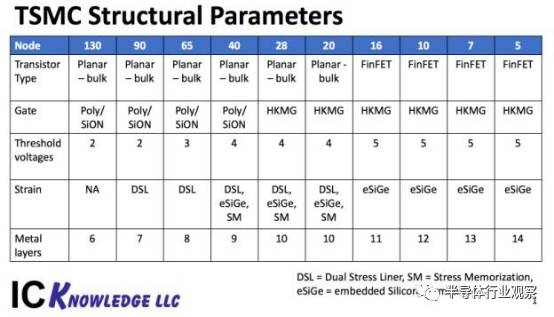

毫無(wú)疑問(wèn)���,晶圓成本在不斷上升。制程的金屬層數(shù)隨著工藝的演進(jìn)不斷上升�����,在130nm時(shí)典型的制程有六層金屬�����,而到了5nm節(jié)點(diǎn)則預(yù)期至少會(huì)有14層金屬�����。

從90nm節(jié)點(diǎn)開(kāi)始開(kāi)始引入應(yīng)力技術(shù)以繼續(xù)增強(qiáng)晶體管的性能��,這也會(huì)增加制程的成本�。從45nm到28nm節(jié)點(diǎn),半導(dǎo)體制程引入了high-k柵技術(shù)以增強(qiáng)性能����。

另一個(gè)變化是晶體管閾值電壓數(shù)目的變化�����。在130nm節(jié)點(diǎn)��,晶體管只有兩種閾值(常規(guī)閾值RVT管與低閾值LVT管)�,而到了16nm之后��,有了多達(dá)五種閾值(超高閾值UHVT�,高閾值HVT�,常規(guī)閾值RVT,低閾值LVT與超低閾值ULVT)�。這是因?yàn)椋瑥?0nm到16/14nm FinFET�����,短溝道效應(yīng)越來(lái)越明顯��,為了控制漏電流必須引入多種閾值的器件��。顯然�,這也會(huì)增加掩膜成本����。

在先進(jìn)半導(dǎo)體制程中,還會(huì)引入新的技術(shù)��,如在16/14nm節(jié)點(diǎn)引入的FinFET技術(shù)��,在5nm引入的堆疊橫向納米線(stacked horizontal nanowire )技術(shù)�。

上圖顯示了不同工藝節(jié)點(diǎn)用到的技術(shù)�����,據(jù)此不同的工藝節(jié)點(diǎn)用到的掩膜層數(shù)如下圖所示:

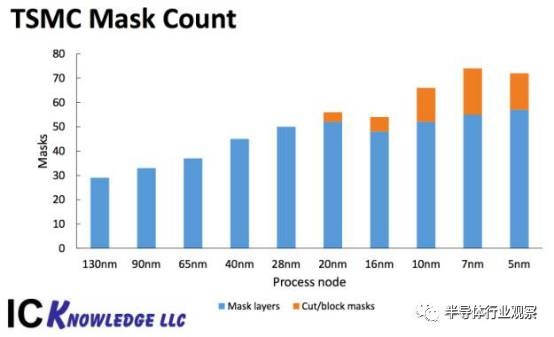

從20nm節(jié)點(diǎn)開(kāi)始��,為了使用傳統(tǒng)光刻技術(shù)實(shí)現(xiàn)更小的特征尺寸��,半導(dǎo)體制程引入了多重pattern技術(shù)�。光刻機(jī)在28nm的時(shí)候只需要一次的光刻曝光就可以實(shí)現(xiàn)了��。

但到了22nm/20nm,單次曝光有時(shí)候就不能給臨界層提供足夠的分辨率����。芯片制造商就通過(guò)多重pattern的方式解決問(wèn)題。這也就是增加了一個(gè)簡(jiǎn)單的兩步流程��。這當(dāng)中的主要的挑戰(zhàn)就是刻這些細(xì)線圖案。

為了達(dá)到目標(biāo)���,芯片制造商只好使用雙重pattern技術(shù)��。在這個(gè)步驟里會(huì)需要兩次光刻和刻蝕步驟去確定一個(gè)單層����。使用這種雙重pattern技術(shù)�����,可以減小30%的pitch�,而三重pattern則需要三次曝光���,也就是需要三次刻蝕步驟����。

除此之外,業(yè)界在10nm和7nm還會(huì)碰到其他問(wèn)題�。在45nm和40nm的時(shí)候����,設(shè)計(jì)的時(shí)候需要用到40層光罩,而到了14nm和10nm�����,光罩的需求量則上升到60層����。“如果沒(méi)有EUV��,只是靠沉浸式去實(shí)現(xiàn)三倍甚至四倍pattern��,那么我們認(rèn)為在7nm的時(shí)候���,光罩?jǐn)?shù)量會(huì)上升到80到85層之間”����。三星的晶圓制造資深主管Kelvin Low表示。

光罩層數(shù)的增加�,也就代表著成本的水漲船高��。同時(shí)覆蓋物也將會(huì)成為Fab的災(zāi)難���。覆蓋物需要把光罩層有秩序的精確地放置在彼此的身上�����。而隨著mask的增加����,覆蓋層也就會(huì)成為噩夢(mèng)。如果沒(méi)對(duì)齊���,覆蓋層問(wèn)題就夠你喝一壺了����。

另外����,現(xiàn)在做一層光罩需要1到1.5天,在7nm的時(shí)候使用多重pattern���,那就需要差不多五個(gè)月的時(shí)間才能做好晶圓���。這就意味著如果繼續(xù)使用多重pattern,會(huì)導(dǎo)致晶圓成本高到無(wú)法接受�����。

除了多重pattern之外���,另一種新的光刻技術(shù)是EUV。然而����,EUV的掩膜制造也十分困難。EUV掩膜在很多方面與傳統(tǒng)193nm光刻的掩膜不一樣�����。因?yàn)樗泻艽蟮母淖?����,?duì)于每個(gè)產(chǎn)品的特性或者功能��,在供應(yīng)鏈中會(huì)產(chǎn)生很大影響���,其中包括光刻膠��、掩膜及中間掩膜���,也涉及制造設(shè)備���,如采用電子束寫(xiě)入設(shè)備以及軟件�����。

在5納米時(shí),掩膜的寫(xiě)入時(shí)間是最大的挑戰(zhàn)����。因?yàn)榻裉斓膯坞娮邮鴮?xiě)入設(shè)備在做復(fù)雜圖形時(shí)的出貨不夠快,費(fèi)時(shí)太久���。從己經(jīng)出爐的報(bào)告來(lái)看��,由于技術(shù)原因��,設(shè)備的研發(fā)用了比預(yù)期長(zhǎng)得多的時(shí)間���。事實(shí)上,任何突破性的創(chuàng)新技術(shù)從研發(fā)到成功���,再達(dá)到量產(chǎn)水平,都是如此���。

另外�����,即使使用EUV�����,多重pattern也是必須的���。只有在真正的關(guān)鍵層才需要采用EUV,而其他層仍然用多重pattern����。可以說(shuō)�,在未來(lái)這樣的混合模式光刻是趨勢(shì)。

而且����,當(dāng)EUV延伸至7納米以下時(shí)���,作為一種提高光刻機(jī)放大倍率的方法���,需要大數(shù)值孔徑的鏡頭(NA),為此ASML已經(jīng)開(kāi)發(fā)了一種變形鏡頭�。它的兩軸EUV鏡頭在掃描模式下能支持8倍放大,而在其他模式下也有4倍�,因此NA要達(dá)0.5至0.6。

由此帶來(lái)的問(wèn)題是EUV光刻機(jī)的吞吐量矛盾���,它的曝光硅片僅為全場(chǎng)尺寸的一半,與今天EUV光刻機(jī)能進(jìn)行全場(chǎng)尺寸的曝光不一樣�。最新 EUV機(jī)器的價(jià)格超過(guò) 1億歐元,是現(xiàn)有常規(guī) 193nm光刻機(jī)價(jià)格的二倍多。

特征尺寸縮小最大的動(dòng)力就是大規(guī)模ASIC中數(shù)字門(mén)尺寸縮小����,從而在相同的芯片面積上可以放下更多的性能更好的標(biāo)準(zhǔn)單元��。最終ASIC的成本應(yīng)當(dāng)同時(shí)考慮晶圓的成本以及門(mén)單元的密度�。

數(shù)字門(mén)單元的尺寸在橫向上決定于多晶硅以及多晶硅通孔的間距,而在縱向上則等于金屬間最小間距乘以track數(shù)目����。Track數(shù)越小���,門(mén)尺寸越小���,但是布線也越困難。

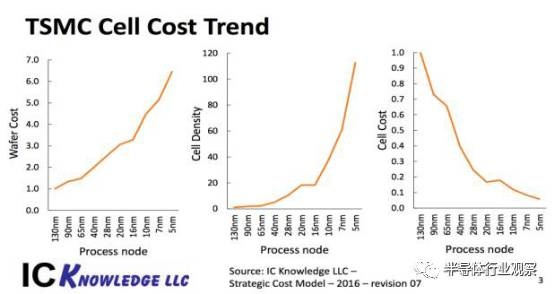

晶圓成本��,數(shù)字門(mén)密度與數(shù)字門(mén)成本如下圖左所示���。在130nm到65nm之間����,晶圓成本上升的速度較慢����,此后在40nm到20nm之間,晶圓成本上升由于加入了更多閾值電壓的晶體管而加快上升����。在20nm之后,晶圓成本上升速度再次加快��,這次是因?yàn)槎嘀豴attern�。

數(shù)字門(mén)密度如下圖中所示����,密度以指數(shù)趨勢(shì)上升,該趨勢(shì)與摩爾定律相符�����。單位數(shù)字門(mén)成本如下圖右所示�,可見(jiàn)從130nm到20nm節(jié)點(diǎn)之間單位門(mén)成本下降較快,但是20nm之后單位門(mén)成本下降速度減緩����。

目前芯片設(shè)計(jì)都有嚴(yán)格的功耗指標(biāo)����。隨著門(mén)單元密度隨指數(shù)上升,單位面積的功率密度也隨指數(shù)上升����,但是芯片散熱能力上升卻沒(méi)這么快。為了解決散熱問(wèn)題��,在芯片上出現(xiàn)了Dark Silicon���,即芯片上部分晶體管在大多數(shù)時(shí)候是不上電的,僅僅在用到的時(shí)候才會(huì)啟動(dòng)�����。

這些Dark Silicon面積包括各類(lèi)加速器����,舉例來(lái)說(shuō)手機(jī)SoC里面的視頻編解碼模塊的電源在不播放視頻的時(shí)候是關(guān)掉的。這些Dark Silicon在大部分時(shí)間是不起作用的��,從另一個(gè)角度說(shuō)Dark Silicon也增加了芯片的成本����。

在先進(jìn)工藝設(shè)計(jì)成本可謂是一飛沖天。這就導(dǎo)致了在先進(jìn)工藝下����,芯片出貨量需要非常大才能抵消NRE成本。如今��,越來(lái)越少的設(shè)計(jì)可以滿足如此大的出貨量�����,因此很多設(shè)計(jì)出于經(jīng)濟(jì)上的考量不再使用最先進(jìn)的工藝���。

盡管先進(jìn)工藝的晶圓成本不斷攀升,門(mén)單元的成本卻能夠保持下降��。然而��,過(guò)高的設(shè)計(jì)成本卻成了一個(gè)問(wèn)題�,只有出貨量非常大的芯片才有機(jī)會(huì)使用最新工藝

競(jìng)爭(zhēng)對(duì)手7nm板上釘釘��,高端市場(chǎng)無(wú)法競(jìng)爭(zhēng)��?

在聯(lián)發(fā)科做出這個(gè)決定的時(shí)候,其競(jìng)爭(zhēng)對(duì)手則在如火如荼推進(jìn)7nm新旗艦打造��。

高通的下一代驍龍?zhí)幚砥魇窃S多關(guān)心手機(jī)的廠商矚目的焦點(diǎn)�����,也接連陸續(xù)有一些爆料以及想像�����。只是�����,最新的一則消息來(lái)源則有點(diǎn)讓人意外�,爆料者來(lái)自于高通自家��,只是出處卻是來(lái)自于蘋(píng)果與高通的專(zhuān)利戰(zhàn)之上�,有人發(fā)現(xiàn)高通提供的其中一則文件,披露了高通下一代旗艦級(jí)處理器驍龍845的存在�����。

隨著高通向美國(guó)國(guó)際貿(mào)易委員會(huì)(ITC)提起訴�����,要求禁止蘋(píng)果iPhone輸美���,高通在提出的一份文件中����,所列出的相關(guān)專(zhuān)利的芯片組����,也讓明年高階款旗艦處理器Snapdragon 845曝光�。

根據(jù)目前的消息,高通下一代旗艦驍龍845會(huì)采用臺(tái)積電的7nm工藝制程�����,不過(guò)也不排除它會(huì)繼續(xù)采用三星的技術(shù)�����。架構(gòu)上�,驍龍845將繼續(xù)沿用自主的8核心設(shè)計(jì),4核A75+4核A55�,GPU則會(huì)升級(jí)到Andreno 630。

至于華為�����,同樣也披露了7nm的計(jì)劃�����。

有網(wǎng)友在微博上爆料稱(chēng)�����,麒麟980處理器已經(jīng)流片�,雖然目前還沒(méi)有更多的信息���,但有消息稱(chēng),可能采用7nm工藝和A75構(gòu)架�����,至于供應(yīng)鏈人士提到的圖形處理有驚喜�����,則可能與傳說(shuō)中的華為自研GPU有關(guān)。

值得一提的是��,消息人士還強(qiáng)調(diào)��,首發(fā)麒麟980處理器的機(jī)型應(yīng)該是P20����,至于為什么不是P11����,或許這是華為早就計(jì)劃好的,之前他們已經(jīng)申請(qǐng)了華為P20的注冊(cè)商標(biāo)�。

不再滿目追擊領(lǐng)先,對(duì)聯(lián)發(fā)科來(lái)說(shuō)�����,也許是一件好事�。